# **PC 62C**

# Enhanced IRQ 16 / 64 Channel Optically Isolated Input Card with Digital I/O

# **User's Manual**

For the IBM AT, PS/2, 386, 486, Pentium, Pentium Pro, ISA and EISA computers

All rights reserved. No part of this Publication may be copied, stored in a retrieval system, or transmitted, in any form by any means, electronic, mechanical, by photocopying, recording, or otherwise, in whole or in part, without prior written permission from the Publishers.

First Edition

January 1998

24 January 1998 Printing

Information furnished in this manual is believed to be accurate and reliable; however no responsibility is assumed for its use, nor for any infringements of patents or other rights of third parties which may result from its use.

IBM, IBM PC/XT/AT and IBM PS/2 are trademarks of International Business Machine Corporation. MicroSoft and MSDOS are trademarks of MicroSoft Corporation. All other trademarks used in this manual are the property of their respective owners.

© Copyright 1998: Shafique Allie (E-mail: shafique@eagle.co.za) Eagle Technology (E-mail: eagle@eagle.co.za) Eagle Web Page: www.eagle.co.za

## **TABLE OF CONTENTS**

| Typical applications.       5         FC 62C Package       5         PC 62C Package consists of:       6         Chapter 1: Installation       7         1.1) Setting the base address.       7         1.2) Wait State Generation on the PC 62C.       9         1.3) Differential/Single-ended External Interrup Lumper Setting.       11         1.4) Interrupt Eable/Disable Umpers.       12         1.5) Connecting the PC 62C to the PC Backplane.       13         CHAPTER 2: Interconnections.       14         2.1) Connections to the IBM AT Bus       14         2.1) Connections to the IBM AT Bus       14         2.1) PC occle DB37 User Connector (P1)       14         2.1) Description of Operation.       15         2.1) Departic Distress       18         CHAPTER 3: Register Structure       19         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL - Global Status Register (offset 1, read/write)       23         3.3) OLCNTRL - Global Control Register (offset 1, read/write)       23         3.4) GATT - RIQ Gaac Control Register (offset 1, read/write)       23         3.5) BUF - Clobal Status Register (offset 1, read/write)       23         3.6) MUXP1 - Local Mux Interrupt Couron Register 2 (offset 12, read/write)                                                                                                                                                      | Introduction                                               |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| PC 62C Package       6         The PC 62C package consists of:       6         Chapter 1: Installation       7         1.1) Setting the base address       7         1.2) Wait State Generation on the PC 62C       9         1.2) Wait State Generation on the PC 62C       9         1.3) Differential/Single-ended External Interrup Jumper Setting       12         1.4) Interrupt Enable/Disable Jumpers       12         1.5) Connecting the PC 62C to the PC Backplane       13         CHAPTER 2: Interconnections       14         2.0) Introduction       14         2.1) Connections to the BM AT Bus       14         2.1) Connections to the BM AT Bus       14         2.1) Description of Operation       15         2.1) Provide UB 10 Interface       17         2.5) Power supply connections       18         CHAPTER 3: Register Structure       19         3.0) Introduction       19         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLONTAL – Global Status Register (offset 1, read/write)       21         3.4) IGATE – IRQ Gac Control Register (offset 1, read/write)       23         3.5) GBUPT – Global Buffer Status Register (offset 10, read/write)       28         3.6) MULXPO – Local Mus Intem                                                                                                                                                                                    |                                                            |  |

| The PC 62C package consists of:       6         Chapter 1: Installation       7         1.1) Setting the base address       7         1.2) Wait State Generation on the PC 62C       9         1.3) Differential Single-ended External Interrupt Jumper Setting       11         1.4) Interrupt Enable/Disable Jumpers       12         1.5) Connecting the PC 62C to the PC Backplane       13         CHAPTER 2: Interconnections       14         2.0) Introduction       14         2.1) Connecting the PC 62C DB37 User Connector (P1)       14         2.1) Connections to the IBM AT Bus       14         2.1) Connections to the IBM AT Bus       14         2.1) Connections to the IBM AT Bus       14         2.2) Description of Operation       14         2.3) Description of Operation       15         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL - Global Status Register (offset 2, read/write)       21         3.3) GLICNTRL - Global Status Register (offset 2, read/write)       23         3.4) GATE - INQ Gate Control Register (offset 4, read/write)       23         3.5) (BULP - Clobal Must Interrupt Control Register (offset 14, read/write)       34         3.1) MUXP1 - Local Mus Interrupt Control Register (offset 14, read/write)       34 <td>Key Features</td> <td></td>                                                                                                    | Key Features                                               |  |

| Chapter 1: Installation       7         1.1) Setting the base address       7         1.2) Wait State Generation on the PC 62C       9         1.3) Differential/Single-ended External Interrup Jumper Setting       12         1.4) Interrupt Endels/Disable Jumpers       12         1.5) Connecting the PC 62C to the PC Backplane       13         CHAPTER 2: Interconnections       14         2.0) Introduction       14         2.1) Connections to the IBM AT Bus.       14         2.1) Connections to the IBM AT Bus.       14         2.1) Decorduction       15         2.4) Digital I/O Interface       17         2.5) Power supply connections       18         CHAPTER 3: Register Structure       19         3.0) Introduction       19         3.0) Introduction       19         3.0) GLOBAL - Global Status Register (offset 0, read only)       20         3.2) GGUP - Global Status Register (offset 10, read/write)       21         3.3) GLOBAL - Global Status Register (offset 10, read/write)       22         3.3) GLOBAL - Global Mus Interrupt Control Register (offset 10, read/write)       23         3.3) GLOBAL - Global Mus Interrupt Control Register (offset 12, read/write)       23         3.1) MUXP1 - Local Mus Interrupt Control Register (offset 2, read only)       28 <td></td> <td></td>                                                                                                                                         |                                                            |  |

| 1.1) Setting the base address       7         1.2) Wait State Generation on the PC 62C       9         1.3) Differential/Single-naded External Interrupt Jumper Setting       11         1.4) Interrupt Enable/Disable Jumpers       12         1.5) Connecting the PC 62C to the PC Backplane       13 <b>CHAPTER 2: Interconnections</b> 14         2.0) Introduction       14         2.1) Connections to the IBM AT Bus       14         2.2) PC 62C DB37 User Connector (P1)       14         2.3) Description of Operation       15         2.4) Digital I/O Interface       17         2.5) Power supply connections       18 <b>CHAPTER 3: Register Structure</b> 19         3.0) Introduction       19         3.0) Introduction       19         3.0) GLORAL – Global Status Register (offset 2, read/write)       20         3.2) GLOBAL – Global Status Register (offset 2, read/write)       21         3.3) GLOUTEN – Objet I/O Register (offset 2, read/write)       23         3.4) BUXP1 – Local Mux Interrupt Control Register (offset 10, read/write)       23         3.7) MUXP1 – Local Mux Interrupt Control Register (offset 10, read/write)       34         3.8) IMUXP2 – Local Mux Interrupt Control Register (offset 10, read/write)       34         3.10) DOTORD1 – Optically Iso                                                                                                                                                                   |                                                            |  |

| 1.2) Wait State Generation on the PC 62C       9         1.3) Differential/Single-ended External Interrupt Jumper Setting       11         1.4) Interrupt Enable/Disable Jumpers       12         1.5) Connecting the PC 62C to the PC Backplane       13         CHAPTER 2: Interconnections       14         2.0) Introduction       14         2.1) Connections to the IBM AT Bus       14         2.1) Connections to the BM AT Bus       14         2.1) Description of Operation       15         2.4) Digital IO Interface       17         2.5) Power supply connections       18         CHAPTER 3: Register Structure       19         3.0) Introduction       20         3.1) OPTORDO - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAT - Clobal States Register (offset 1, read/write)       20         3.3) GRUTF - Global Uffer Status Register (offset 1, read/write)       21         3.3) GRUTP - Local Mux Interrupt Control Register (offset 1, read/write)       23         3.3) (BUXPO - Local Mux Interrupt Control Register (offset 1, read/write)       31         3.4) (DATE - Interrupt Security Register 3 (offset 14, read/write)       34         3.5) (BUVF - Local Mux Interrupt Control Register (offset 2, read only)       38         3.6) (DIV - Diciall Volated Input Port Register 3                                                                                                              | Chapter 1: Installation                                    |  |

| 1.3) Differential/Single-ended External Interrupt Jumper Setting.       11         1.4) Interrupt Enable/Disable Jumpers       12         1.5) Connecting the °C 63°C to the °C Backplane.       13 <b>CHAPTER 2: Interconnections</b> 14         2.0) Introduction       14         2.1) Connections to the IBM AT Bus       14         2.1) Connections to the IBM AT Bus       14         2.3) Description of Operation       15         2.4) Digital I/O Interface       17         2.5) Power supply connections       18         3.0) Introduction       19         3.0) Introduction       19         3.0) Introduction       20         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLONAL - Global Control Register (offset 1, read/write)       21         3.3) GLCNTRL - Global Control Register (offset 1, read/write)       23         3.4) (GATE - IRQ Gate Control Register (offset 1, read/write)       28         3.6) (MUXPD - Local Mux Interrupt Control Register (offset 1, read/write)       33         3.8) IMUXP2 - Local Mux Interrupt Control Register (offset 1, read/write)       33         3.10) DOT Digital I/O Register (offset 1, read/write)       34         3.110 DOTRDD 1 - Optically Isolated Input Port Register 1 (offset 2, read only)       34 <td></td> <td></td>                                                                                                               |                                                            |  |

| 1.4) Interrupt Enable/Disable Jumpers       12         1.5) Connecting the PC 62C to the PC Backplane       13 <b>CHAPTER 2: Interconnections</b> 14         2.0) Introduction       14         2.1) Connections to the IBM AT Bus       14         2.1) Connections to the IBM AT Bus       14         2.1) Connections to the IBM AT Bus       14         2.1) Degrat IO Interface       15         2.4) Digital IO Interface       17         2.5) Power supply connections       18 <b>CHAPTER 3: Register Structure</b> 19         3.0) Introduction       20         3.0) Introduction       20         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL – Global Status Register (offset 4, read/write)       21         3.3) GLCMTR       230 (Introduction       23         3.4) INTRUE – IRQ Gate Control Register (offset 10, read/write)       21         3.4) IGATE – IRQ Gate Control Register (offset 10, read/write)       23         3.6) IMUXP1 – Local Mux Interrupt Control Register (offset 11, read/write)       34         3.7) IMUXP1 – Local Mux Interrupt Control Register (offset 12, read/write)       36         3.8) IMUXP1 – Local Mux Interrupt Control Register (offset 12, read/write)       37         3.1                                                                                                                                                                            |                                                            |  |

| 1.5) Connecting the PC 62C to the PC Backplane.       13 <b>CHAPTER 2: Interconnections</b> 14         2.0) Introduction.       14         2.1) Connections to the IBM AT Bus.       14         2.3) Description of Operation.       14         2.3) Description of Operation.       15         2.4) Digital I/O Interface.       17         2.5) Power supply connections.       18 <b>CHAPTER 3: Register Structure</b> 19         3.0) Introduction.       20         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only).       20         3.2) GLOBAL – Global Status Register (offset 4, read/write).       21         3.3) GLOTTE – IRQ Gate Control Register (offset 4, read/write).       23         3.4) (GATE – IRQ Gate Control Register (offset 4, read/write).       23         3.5) (BUUP – Local Mux Interrupt Control Register 2 (offset 10, read/write).       28         3.6) (MUXP) – Local Mux Interrupt Control Register 2 (offset 10, read/write).       36         3.10) DIO – Digital I/O Register (offset 18, read / write).       36         3.11) OPTORD - Optically Isolated Input Port Register 1 (offset 24, read only).       37         3.13) OPTORD - Optically Isolated Input Port Register 1 (offset 24, read only).       38         3.11) OPTORD - Optically Isolated Input Port Register 2 (offset 24, read only). <td></td> <td></td>                                                                            |                                                            |  |

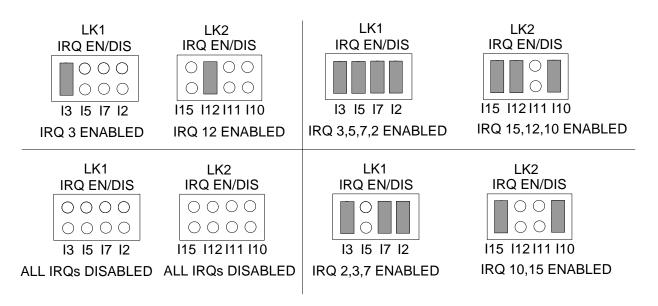

| CHAPTER 2: Interconnections       14         2.0) Introduction       14         2.1) Connections to the IBM AT Bus       14         2.2) PC 62C DB37 User Connector (P1)       14         2.3) Description of Operation       15         2.4) Digital I/O Interface       17         2.5) Power supply connections       18         CHAPTER 3: Register Structure       19         3.0) Introduction       19         3.0) OPTORD0 - Optically Isolated Input Port Register (offset 0, read/write)       20         3.2) GLOBAL - Global Status Register (offset 4, read/write)       21         3.3) GLCNTRL - Global Control Register (offset 6, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 6, read/write)       28         3.5) GBUF - Global Buffer Status Register (offset 16, read/write)       28         3.6) INUXP0 - Local Mux Interrupt Control Register (offset 14, read/write)       34         3.9) INUXP1 - Local Mux Interrupt Control Register (offset 14, read/write)       34         3.0) DINO Dipital I/O Register (offset 18, read/write)       34         3.0) DINO Dipital I/O Register (offset 14, read/write)       36         3.10) DITO Dipital I/O Register (offset 10, read/write)       37         3.11) DPTORD1 - Optically Isolated Input Port Register 1 (offset 12, read only)       38 <td< td=""><td>1.4) Interrupt Enable/Disable Jumpers</td><td></td></td<>                                             | 1.4) Interrupt Enable/Disable Jumpers                      |  |

| 2.0) Inroduction       14         2.1) Connections to the IBM AT Bus.       14         2.1) Connections to the IBM AT Bus.       14         2.2) PC 62C DB37 User Connector (P)       14         2.3) Description of Operation       15         2.4) Digital ICO Interface       17         2.5) Power supply connections.       18 <b>CHAPTER 3: Register Structure</b> 19         3.0) Introduction       19         3.0) Introduction Control Register (offset 0, read/write)       20         3.2) GLOBAL - Global Status Register (offset 6, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 1, read/write)       23         3.6) IMUXPD - Local Mux Interrupt Control Register (offset 12, read/write)       23         3.6) IMUXPD - Local Mux Interrupt Control Register (offset 12, read/write)       34         3.8) IMUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.10) DTO DD1 - Optically Isolated Input Port Register 3 (offset 12, read/write)       36         3.10) DTOPD1 - Optically Isolated Input Port Register 2 (offset 22, read only)       38         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 22, read only)       38         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.11) OPTORD1 - Optically Isolated In                                                                                    |                                                            |  |

| 2.1) Connections to the IBM AT Bus       14         2.2) PC 62C DB37 User Connector (P1)       14         2.3) Description of Operation       15         2.4) Digital I/O Interface       17         2.5) Power supply connections       18         CHAPTER 3: Register Structure         9       30) Introduction       19         3.0) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLONAL - Global Status Register (offset 4, read/write)       21         3.3) GLCNTRL - Global Buffer Status Register (offset 4, read/write)       23         3.4) GATE - IRQ Gate Control Register (offset 4, read/write)       23         3.6) IMUXP0 - Local Mux Interrupt Control Register 2 (offset 12, read/write)       34         3.7) TIMUXP1 - Local Mux Interrupt Control Register 2 (offset 14, read/write)       34         3.9) ISETX - Interrupt SetReset Register (offset 7, read/write)       36         3.10) DIO - Digital I/O Register (offset 20, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 22, read only)       39         3.12) OPTORD2 - Optically Isolated Input Port Register 3 (offset 14, read/write)       34         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 24, read only)       39         3.13) OPTORD4 - Optically Isolated Input Port Register 3 (offset 24, read only                                                    |                                                            |  |

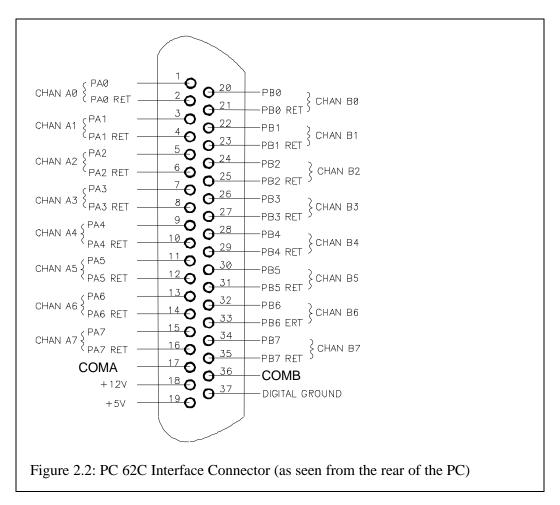

| 2.2) PC 62C DB37 User Connector (P1)       14         2.3) Description of Operation       15         2.4) Digital I/O Interface       17         2.5) Power supply connections       18 <b>CHAPTER 3: Register Structure</b> 19       30.1 Introduction         30.1) Introduction       19         31.1 OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         32.3) GLOBAL - Global Status Register (offset 1, read/write)       21         33.3) GLCNTRL - Global Control Register (offset 1, read/write)       21         34.1 GATE - IRQ Gate Control Register (offset 1, read/write)       28         35.6 IBUFF - Global Buffer Status Register (offset 10, read/write)       28         36.1 MUXP0 - Local Mux Interrupt Control Register (offset 12, read/write)       36         38.1 MUXP1 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       36         39.1 SIETX - Interrupt Set/Reset Register (offset 18, read / write)       36         310 D DTORD1 - Optically Isolated Input Port Register 1 (offset 22, read only)       38         311) OPTORD2 - Optically Isolated Input Port Register 1 (offset 24, read only)       39         313) OPTORD3 - Optically Isolated Input Port Register 1 (offset 24, read only)       39         313) OPTORD1 - Optically Isolated Input Port Register 1 (offset 24, read only)       38 <td></td> <td></td>                                                        |                                                            |  |

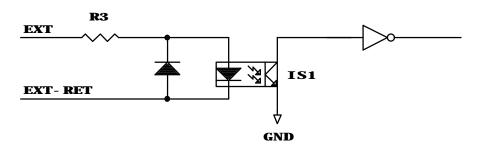

| 2.3) Description of Operation.       15         2.4) Digital I/O Interface       17         2.5) Power supply connections.       18 <b>CHAPTER 3: Register Structure</b> 19         3.0) Introduction       19         3.1) OPTORDO - Optically Isolated Input Port Register (offset 0, read only)       20         2.2) GLOBAL - Global Status Register (offset 2, read/write)       20         3.3) GLCNTRL - Global Control Register (offset 4, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 5, read only)       28         3.5) GBUF - Global Buffer Status Register (offset 7, read/write)       23         3.6) INUXPO - Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.7) INUXP1 - Local Mux Interrupt Control Register 2 (offset 14, read/write)       34         3.8) INUXP2 - Local Mux Interrupt Control Register 2 (offset 12, read/write)       36         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.10) DD O - Digital I/O Register (offset 12, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 12, read only)       38         3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13)                                                             |                                                            |  |

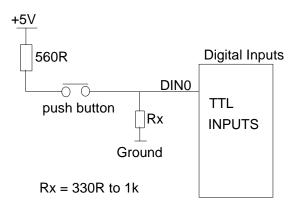

| 2.4) Digital I/O Interface       17         2.5) Power supply connections       18         CHAPTER 3: Register Structure       19         3.0) Introduction       19         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL - Global Status Register (offset 4, read/write)       21         3.3) GLCNTRL - Global Control Register (offset 4, read/write)       23         3.5) GBUF - Global Buffer Status Register (offset 7, read only)       28         3.5) GBUF - Global Suffer Status Register (offset 10, read/write)       28         3.5) GBUF - Clobal Mux Interrupt Control Register (offset 110, read/write)       28         3.6) INUXPO - Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.8) INUXP2 - Local Mux Interrupt Control Register 3 (offset 12, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read/write)       35         3.10) DFO Digital I/O Register (offset 18, read/write)       36         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 22, read only)       38         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       34         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolat                                        |                                                            |  |

| <b>CHAPTER 3: Register Structure</b> 19         3.0) Introduction       19         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL - Global Status Register (offset 4, read/write)       20         3.3) GLCNTRL - Global Control Register (offset 4, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 8, read only)       28         3.5) GBUF - Global Buffer Status Register (offset 8, read only)       28         3.5) GBUF - Global Mux Interrupt Control Register (offset 10, read/write)       29         3.7) INUXP1 - Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.8) INUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) INETX - Interrupt Set/Reset Register (offset 20, read / write)       36         3.10) DIO - Digital I/O Register (0ffset 20, read / write)       36         3.11) OPTORD1 - Optically Isolated Input Port Register 1 (offset 22, read only)       39         3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD4 - Optically Isolated Input Port Register 2 (offset 24, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41                                  |                                                            |  |

| 3.0) Introduction       19         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL - Global Status Register (offset 2, read/write)       20         3.3) GLCNTRL - Global Control Register (offset 4, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 8, read only)       28         3.5) GBUF - Global Buffer Status Register (offset 8, read only)       28         3.6) IMUXPO - Local Mux Interrupt Control Register 2 (offset 10, read/write)       29         3.7) IMUXP1 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.8) IMUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.10) DIO - Digital I/O Register (offset 19, read / write)       36         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 22, read only)       38         3.12) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Introduction       41                                            | 2.5) Power supply connections                              |  |

| 3.0) Introduction       19         3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL - Global Status Register (offset 2, read/write)       20         3.3) GLCNTRL - Global Control Register (offset 4, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 8, read only)       28         3.5) GBUF - Global Buffer Status Register (offset 8, read only)       28         3.6) IMUXPO - Local Mux Interrupt Control Register 2 (offset 10, read/write)       29         3.7) IMUXP1 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.8) IMUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.10) DIO - Digital I/O Register (offset 19, read / write)       36         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 22, read only)       38         3.12) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Introduction       41                                            | CHAPTER 3: Register Structure                              |  |

| 3.1) OPTORD0 - Optically Isolated Input Port Register (offset 0, read only)       20         3.2) GLOBAL - Global Status Register (offset 2, read/write)       21         3.3) GLCNTRL - Global Control Register (offset 4, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 8, read only)       23         3.6) INUXPO - Local Mux Interrupt Control Register (offset 10, read/write)       29         3.7) INUXP1 - Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.8) INUXP2 - Local Mux Interrupt Control Register 2 (offset 14, read/write)       36         3.9) ISETX - Interrupt SerKeset Register (offset 18, read / write)       36         3.10) DIO - Digital I/O Register (offset 20, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 1 (offset 24, read only)       38         3.12) OPTORD2 - Optically Isolated Input Port Register 3 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 24, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Normal Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mod     |                                                            |  |

| 3.3) GLCNTRL - Global Control Register (offset 4, read/write)       21         3.4) IGATE - IRQ Gate Control Register (offset 8, read only)       28         3.5) GBUF - Global Buffer Status Register (offset 10, read/write)       29         3.6) IMUXP0 - Local Mux Interrupt Control Register 2 (offset 10, read/write)       31         3.8) IMUXP1 - Local Mux Interrupt Control Register 2 (offset 11, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 8, read / write)       36         3.0) DIO - Digital I/O Register 2 (offset 18, read / write)       36         3.10) DTORD1 - Optically Isolated Input Port Register 1 (offset 22, read only)       38         3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software       46         5.1) Board Handles       46         5.2) Interrupt functions                                                                                  |                                                            |  |

| 3.4) IGATE - IRQ Gate Control Register (offset 6, read/write)       23         3.5) GBUF - Global Buffer Status Register (offset 8, read only)       28         3.6) IMUXP0 - Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.6) IMUXP1 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       31         3.8) IMUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.10) DIO - Digital I/O Register (offset 20, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 1 (offset 22, read only)       38         3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the POto-Isolators using Polled I/O       42         4.2) Reading the Opto-Isolators using Normal Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software       46 <tr< td=""><td></td><td></td></tr<> |                                                            |  |

| 3.5) GBUF – Global Buffer Status Register (offset 8, read only)       28         3.6) IMUXP0 – Local Mux Interrupt Control Register (offset 10, read/write)       29         3.7) IMUXP1 – Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.8) IMUXP2 – Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) ISETX – Interrupt SetReset Register (offset 18, read / write)       36         3.10) DIO – Digital I/O Register (offset 20, read / write)       37         3.11) OPTORD1 – Optically Isolated Input Port Register 1 (offset 22, read only)       38         3.12) OPTORD2 – Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 – Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Namal Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Namal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software       46         5.1) Board Handles       46         5.1) Board Handles       50         6.1) Testing the P                                                                           |                                                            |  |

| 3.6) IMUXP0 - Local Mux Interrupt Control Register 2 (offset 10, read/write)       29         3.7) IMUXP1 - Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.8) IMUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.0) DIO - Digital I/O Register 20, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 2 (offset 22, read only)       38         3.20 OPTORD2 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       39         3.10 DPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software       46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C                                                                                  |                                                            |  |

| 3.7) IMUXP1 - Local Mux Interrupt Control Register 2 (offset 12, read/write)       31         3.8) IMUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.10) DIO - Digital I/O Register (offset 20, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 1 (offset 22, read only)       38         3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C       50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51 <td></td> <td></td>                                                                   |                                                            |  |

| 3.8) IMUXP2 - Local Mux Interrupt Control Register 3 (offset 14, read/write)       34         3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.10) DIO - Digital I/O Register (offset 20, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 1 (offset 22, read only)       38         3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Normal Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C       50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51         Chapter 7: Troubleshooting       52         Chapter 8: Repair                                                                                                               |                                                            |  |

| 3.9) ISETX - Interrupt Set/Reset Register (offset 18, read / write)       36         3.10) DIO - Digital I/O Register (offset 20, read / write)       37         3.11) OPTORD1 - Optically Isolated Input Port Register 1 (offset 22, read only)       38         3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40 <b>Chapter 4: Programming Guide</b> 41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       45 <b>Chapter 5: Driver Software</b> 46         5.1) Board Handles       46         5.2) Interrupt functions Reference       48 <b>Chapter 6: Testing the PC 62C</b> 50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51 <b>Chapter 7: Troubleshooting</b> 52 <b>Chapter 8: Repair Service</b> 54         Specifications       55                                                                                                                                                                                        |                                                            |  |

| 3.10) DIO – Digital I/O Register (offset 20, read / write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                            |  |

| 3.12) OPTORD2 - Optically Isolated Input Port Register 2 (offset 24, read only)       39         3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C       50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51         Chapter 7: Troubleshooting       52         Chapter 8: Repair Service       54         Specifications       55         Appendix A (Base Address Settings)       58                                                                                                                                                                                                                                                                                                                                                                          | 3.10) DIO – Digital I/O Register (offset 20, read / write) |  |

| 3.13) OPTORD3 - Optically Isolated Input Port Register 3 (offset 26, read only)       40         Chapter 4: Programming Guide       41         4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       43         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software       46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C       50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51         Chapter 7: Troubleshooting       52         Chapter 8: Repair Service       54         Specifications       55         Appendix A (Base Address Settings)       58                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |  |

| Chapter 4: Programming Guide414.0) Introduction414.1) Initialising the PC62C424.2) Reading the Opto-Isolators using Polled I/O424.3) Configuring the Opto-Isolators using Shared Interrupt Mode434.4) Configuring the Opto-Isolators using Normal Interrupt Mode434.5) Reading the Digital I/O Lines45Chapter 5: Driver Software465.1) Board Handles465.2) Interrupt functions475.3) Quick Function Reference48Chapter 6: Testing the PC 62C506.1) Testing the PC 62C Board506.2) Connecting Normally Open devices to the Digital Input Lines51Chapter 7: Troubleshooting52Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                            |  |

| 4.0) Introduction       41         4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       43         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software       46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C       50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51         Chapter 7: Troubleshooting       52         Chapter 8: Repair Service       54         Specifications       55         Appendix A (Base Address Settings)       58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                            |  |

| 4.1) Initialising the PC62C       42         4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       43         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software         46       5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C         50       6.1) Testing the PC 62C Board       50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51         Chapter 7: Troubleshooting         S2         Chapter 8: Repair Service         S4         Specifications         S5         Address Settings)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Chapter 4: Programming Guide                               |  |

| 4.2) Reading the Opto-Isolators using Polled I/O       42         4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software         4.6       5.1) Board Handles       46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48         Chapter 6: Testing the PC 62C         6.1) Testing the PC 62C Board       50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51         Chapter 7: Troubleshooting         Chapter 8: Repair Service         Specifications          Specificat                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            |  |

| 4.3) Configuring the Opto-Isolators using Shared Interrupt Mode       43         4.4) Configuring the Opto-Isolators using Normal Interrupt Mode       44         4.5) Reading the Digital I/O Lines       45         Chapter 5: Driver Software         46       5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference.       48         Chapter 6: Testing the PC 62C         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51         Chapter 7: Troubleshooting         Chapter 8: Repair Service         Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                            |  |

| 4.4) Configuring the Opto-Isolators using Normal Interrupt Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                            |  |

| 4.5) Reading the Digital I/O Lines       45 <b>Chapter 5: Driver Software</b> 46         5.1) Board Handles       46         5.2) Interrupt functions       47         5.3) Quick Function Reference       48 <b>Chapter 6: Testing the PC 62C</b> 50         6.1) Testing the PC 62C Board       50         6.2) Connecting Normally Open devices to the Digital Input Lines       51 <b>Chapter 7: Troubleshooting</b> 52 <b>Chapter 8: Repair Service</b> 54         Specifications       55         Appendix A (Base Address Settings)       58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                            |  |

| Chapter 5: Driver Software465.1) Board Handles465.2) Interrupt functions475.3) Quick Function Reference48Chapter 6: Testing the PC 62C506.1) Testing the PC 62C Board506.2) Connecting Normally Open devices to the Digital Input Lines51Chapter 7: Troubleshooting52Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |  |

| 5.1) Board Handles465.2) Interrupt functions475.3) Quick Function Reference48Chapter 6: Testing the PC 62C6.1) Testing the PC 62C Board506.2) Connecting Normally Open devices to the Digital Input Lines51Chapter 7: Troubleshooting5252Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                            |  |

| 5.2) Interrupt functions475.3) Quick Function Reference48Chapter 6: Testing the PC 62C6.1) Testing the PC 62C Board506.1) Testing the PC 62C Board506.2) Connecting Normally Open devices to the Digital Input Lines51Chapter 7: Troubleshooting52Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                            |  |

| 5.3) Quick Function Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                            |  |

| Chapter 6: Testing the PC 62C506.1) Testing the PC 62C Board506.2) Connecting Normally Open devices to the Digital Input Lines51Chapter 7: Troubleshooting52Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                            |  |

| 6.1) Testing the PC 62C Board506.2) Connecting Normally Open devices to the Digital Input Lines51Chapter 7: Troubleshooting52Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                            |  |

| 6.2) Connecting Normally Open devices to the Digital Input Lines51Chapter 7: Troubleshooting52Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                            |  |

| Chapter 7: Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                            |  |

| Chapter 8: Repair Service54Specifications55Appendix A (Base Address Settings)58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                            |  |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 7: Troubleshooting                                 |  |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 8: Repair Service                                  |  |

| Appendix A (Base Address Settings)    58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                          |  |

| Appendix B (PC62C Template)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Appendix A (Base Address Settings)                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Appendix B (PC62C Template)                                |  |

# Introduction

The PC 62C is an enhanced IRQ Optical Isolated Input Board for the IBM PC/XT/AT, 486, Pentuim, ISA and EISA Computers. It provides 16 / 64 Optically Isolated Inputs in either single ended or differential mode.

16 Digital Inputs and 16 Digital Outputs (with open collector outputs) are also provided on the PC62C.

The PC 62C fits into one of the IBM PC/AT, ISA, EISA expansion slot.

### **Typical applications**

Industrial control Process Control Laboratory Automation Energy management Product testing

### **Key Features**

- 16 channel Optically isolated inputs expandable to 48

- Background readback of Isolated Input lines via Interrupt Mode

- IRQ Mode via shared interrupts or individual interrupt lines

- Ideal Card for multitasking environments

- Status of isolated lines is only read when there is a state change in IRQ Mode

- Host CPU time kept to a minimum

- 16 Bit Reads/Writes supported to provide higher thruputs

- Interrupt selection IRQ2 thru IRQ15 can be automatically changed via software

- Isolated inputs can be fed directly into the IRQ Bus system or toggled via Global Register System

- Pin for Pin compatible with PC 62B Optically Isolated Input Card

- 450V RMS Min / 2kV Max Isolation Voltage

- Built-in Wait state generation for fast Bus clock speeds

- Frequency response up to 10kHz

- Address selectable